CITIROC 1A

Citiroc 1A is a 32-channel front-end ASIC designed to readout silicon photo-multipliers (SiPM) for scientific instrumentation application.

Citiroc 1A allows triggering down to 1/3 pe and provides the charge measurement with a good noise rejection. Moreover, Citiroc 1A outputs the 32-channel triggers with a high resolution timing (better than 100 ps).

An adjustment of the SiPM high-voltage is possible using a channel-by-channel DAC connected to the ASIC inputs. That allows a fine SiPM gain and dark noise adjustment at the system level to correct for the non-uniformity of SiPMs.

CITIROC 1A can be calibrated using a unique calibration signal.

Timing measurement better than 100 ps RMS jitter is measured on single photo-electron along with 1% linearity energy measurement up to 2500 p.e. The power consumption is 225mW/ASIC when all stages are ON.

|

TRL Technology Readiness Level |

8 - Full system using ASIC running |

|

Available versions |

Citiroc 1A : available |

|

Detector Read-Out |

SiPM, SiPM array |

|

Number of Channel |

32 |

|

Signal Polarity |

Positive |

|

Sensitivity |

Trigger on 1/3 photo-electron |

|

Timing Resolution |

better than 100ps RMS on single photo-electron |

|

Dynamic Range |

0-400 pC i.e 2500 photo-electrons @ 106 SiPM gain |

|

Packaging & Dimension |

|

|

Power Consumption |

225 mW when all stages on - supply voltage 3.3V |

|

Inputs |

32 voltage inputs with independant SiPM HV adjustments |

|

Outputs |

|

|

Internal Programmable Features |

|

|

Evaluation systems |

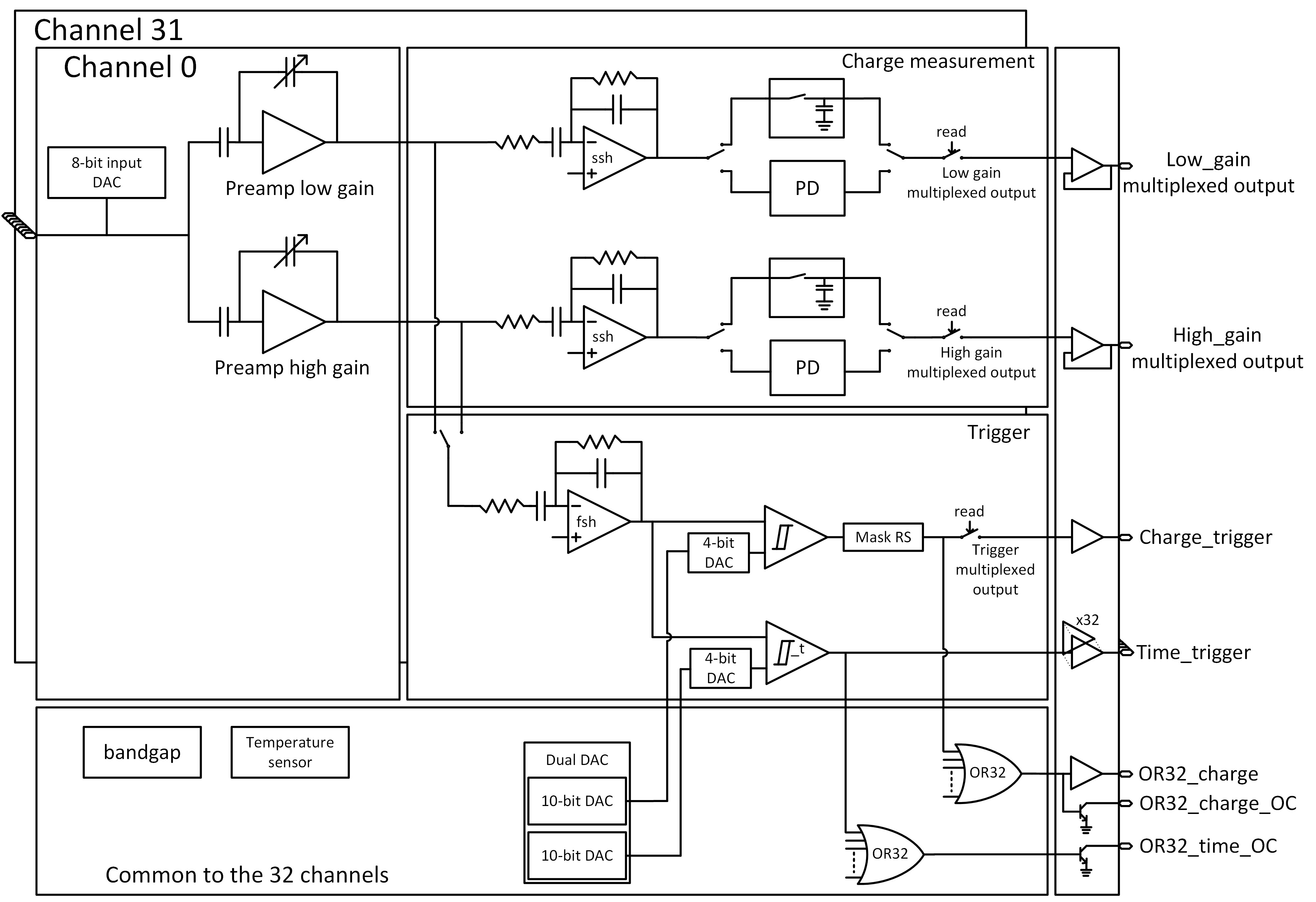

The following figure shows the diagram relating to the main signal conditioning blocks of a CITIROC 1A channel

Each CITIROC is characterized by separate chains for high gain (HG), low gain (LG) and trigger outputs. Each CITIROC channel implements an 8-bit DAC for SiPM gain adjustment. The pulse generated by the SiPM is processed by the AC coupled

CITIROC electronic channel. It is amplified by means of two programmable preamplifiers and then shaped with two shaper circuits (LG and HG) respectively. The gain values have been chosen to obtain a dynamic range from 0 to about 60 photoelectrons for the HG channel and from 0 to about 2000 photoelectrons for the LG channel. A bipolar fast shaper (FSH) connected to the high gain preamplfier produces a fast signal (~15 ns shaping time) that is connected to a discriminator with a 10 bits-DAC programmable threshold. The output of the discriminator gives a digital signal (trigger) if the input signal exceeds the threshold level.

The peak detector or single channel analyzer (track&hold mode) are selectable via slowcontrol configuration bits. The base-line operational mode is peak detector. Peak detector captures the most positive point of the input signal so that the maximum of the shapers signals represents the pulse height conversion of the SiPM output signal. The digital triggers are available on the 32 + 32 output pads of the two ASICs constituting the unit module based on 64 pixels. The analog outputs of the peak detectors are stored into 64 analog memories and read, at the occurrence of a trigger condition, by multiplexing the three-state output registers (LG and HG respectively) and then converted to digital counts by external ADC devices. The Artix 7 FPGA manages all the input/output operations from/to CITIROCs and SiPMs.