Intensified Active Pixel Sensor (IAPS)

Un nuovo tipo di sensore di posizione (sensore di pixel attivi a semiconduttore di ossido di metallo complementare o CMOS-APS) utilizzato come sistema di lettura nei contatori di fotoni intensificati basati su MCP, è stato utilizzato nel nostro laboratorio alcuni anni fa con buon successo.

La tecnologia CMOS, consente di integrare "on chip" l'indirizzamento dei pixel e i circuiti di lettura, nonché i convertitori da analogico a digitale. La struttura altamente parallela dell'APS consente una gamma dinamica di conteggio maggiore di quella ottenibile con i sistemi di conteggio dei fotoni basati su un CCD intensificato. Altre due importanti caratteristiche, fondamentali nelle applicazioni spaziali, devono essere aggiunte: i dispositivi CMOS utilizzano un singolo alimentatore da 3,3 V e mostrano una migliore durezza delle radiazioni rispetto ai CCD.

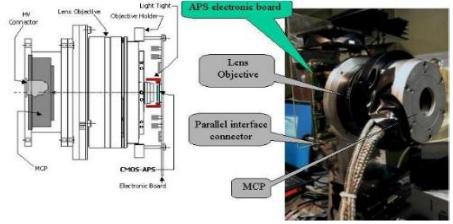

La tecnologia CCD, sviluppata più di venti anni fa e migliorata in questi anni, è ben nota ed è apprezzata in molti campi per l'elevata efficienza quantistica e il basso rumore di lettura anche a velocità di scansione relativamente elevate. La nuova tecnologia CMOS-APS è in continua evoluzione e, al momento, un rumore di lettura leggermente più alto caratterizza questa tecnologia. Ma questo parametro, nei sistemi di conteggio dei fotoni può essere superato impostando un guadagno MCP più elevato. L'altra differenza, a favore del CCD, è il fattore di riempimento che mentre per il CCD è del 100%, per il CMOS-APS non è superiore al 60%. Tuttavia, questo parametro non è molto critico per le prestazioni dei sistemi intensificati. Il sistema sviluppato è sostanzialmente costituito da una Micro Channel Plate (MCP) con uno schermo al fosforo accoppiato a un CMOS-APS attraverso un'ottica a relè. Uno schema a blocchi del sistema completo è mostrato in figura.

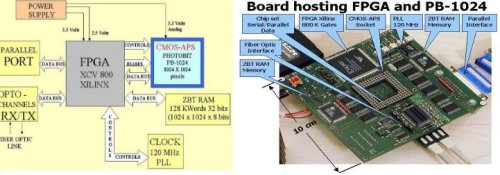

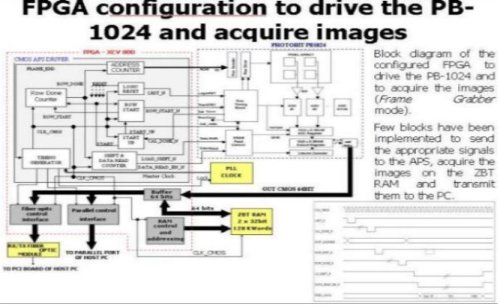

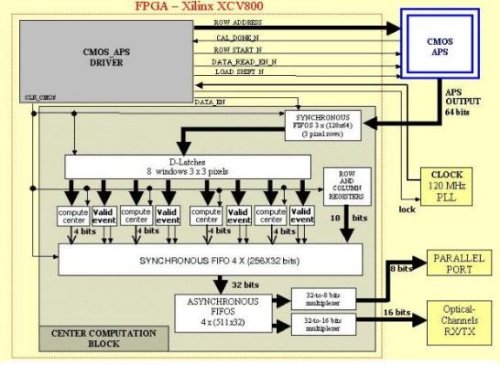

Gli elettroni generati in un fotocatodo vengono moltiplicati per l'MCP e la nuvola di elettroni emergenti colpisce su uno schermo di fosforo che fornisce un punto luminoso. Un'ottica a relè ri-immagini questo punto sul CMOS-APS. L'APS e un FPGA (Field Programmable Gate Array) ad alta densità si trovano sulla stessa scheda collegata a un PC tramite un'interfaccia parallela e una connessione seriale veloce (1,2 GBit / s) basata su fibra ottica. L'FPGA è configurato per pilotare l'APS, leggere i pixel ed eseguire calcoli. Le varie funzioni si ottengono scaricando il file di configurazione tramite l'interfaccia parallela utilizzando un protocollo standard o tramite le fibre ottiche utilizzando una DLL dedicata. Infine, i dati corrispondenti alle coordinate di ciascun evento valido vengono acquisiti dal computer e memorizzati in un file.

LAYOUT OTTICO E MECCANICO

|

Il CMOS-APS viene solitamente fornito coperto con una finestra e, come per i CCD, abbiamo pianificato di sostituire la finestra con una conicità a fibra ottica. Per i primi test abbiamo deciso di utilizzare un obiettivo ottico, il modello Rodenstock HR-Heligaron 35, con un'apertura numerica molto piccola (per una migliore risoluzione spaziale) e pochi componenti ottici (per ridurre al minimo la perdita di segnale dovuta alla trasmittanza di ciascun elemento) . La figura mostra a sinistra il layout meccanico e a destra un'immagine dell'intero sistema. |

IL CMOS-APS

|

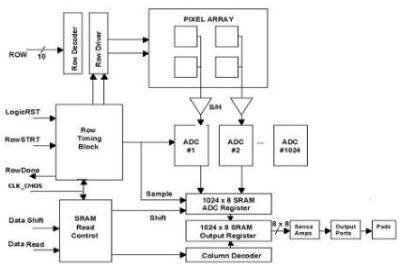

Come sensore di posizione del sistema di conteggio dei fotoni abbiamo utilizzato il CMOS-APS PB-1024 prodotto da Photobit che, con 500 frame / s, garantisce un elevato tasso di conteggio e quindi aumenta la gamma dinamica del sistema. L'architettura interna è mostrata in figura. Il PB-1024 è stato progettato per avere un parallelismo delle righe di pixel, infatti pb1024 include su chip i circuiti di temporizzazione e controllo per trattare una riga alla volta (vedere il Blocco di sincronizzazione riga sullo schema) e 1024 8 bit-A / D converte per digitalizzare contemporaneamente il segnale analogico da un'intera riga di pixel. Inoltre, il chip contiene speciali circuiti di auto-calibrazione che consentono di ridurre il rumore del pattern fisso. Per accelerare l'output dei dati viene utilizzato un array di memoria "ping pong". Questo tipo di memoria memorizza i dati digitalizzati a 10 bit a 8 bit e viene letto durante il successivo ciclo di conversione. Otto pixel (una parola di 64 bit di larghezza) alla volta possono essere letti attraverso le otto porte di 8 bit. Pertanto in 128 impulsi di clock viene letta un'intera riga. Il dispositivo può essere considerato un "dispositivo digitale", nel senso che riceve segnali digitali e invia dati digitalizzati. Pertanto, per pilotare il sensore è necessario solo un “controller digitale”, come un array di logica programmabile sul campo (FPGA). |

L'ELETTRONICA DI CONTROLLO

|

Lo schema a blocchi dell'elettronica frontale del rivelatore è mostrato nel pannello di sinistra di questa figura, mentre un'immagine della scheda elettronica è nel pannello di destra. L'APS ha su chip quasi tutta l'elettronica necessaria per funzionare come un imager, l'FPGA fornisce il resto dei segnali necessari. I circuiti implementati sull'FPGA forniscono i segnali di polarizzazione, la loro telemetria, quella dell'alimentazione e l'interfaccia al PC host. Una RAM ZBT a 128 bit di 128 parole viene utilizzata per memorizzare l'immagine acquisita per essere successivamente letta ad una diversa velocità di dati. Ad esempio per guidare il CMOS-APS come semplice frame grabber è stato implementato un semplice circuito sull'FPGA: |

|

Il cuore del controller è costituito dall'implementazione sull'algoritmo FPGA dell'algoritmo centroide, che è essenzialmente diviso in due parti: la convalida dell'evento, che consiste nel localizzare il segnale di picco di tutti gli eventi al di sopra di uno specifico livello di discriminazione, e il calcolo del centroide , che esegue un baricentro troncato a tre punti: se i valori dei pixel sono a, b, c, con b che è il più alto, la coordinata del centro sarà (ca) / (a + b + c). La figura seguente mostra lo schema a blocchi del circuito implementato. |

|

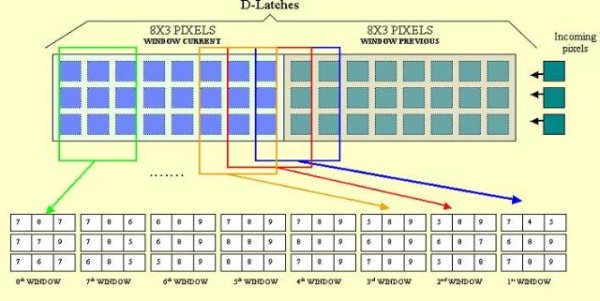

I dati a 64 bit, corrispondenti a 8 pixel, sono memorizzati su FIFO sincroni ad ogni impulso di CLK_CMOS e quando le prime tre righe sono completamente impaccate su FIFO, la procedura di calcolo continua. Una serie di D-Latch viene utilizzata per ottenere 8 finestre di 3X3 pixel. Il calcolo centrale e i circuiti di convalida dell'evento operano simultaneamente su queste 8 finestre e, ad ogni impulso di clock, altre otto finestre da 3x3 pixel sono memorizzate nei D-Latch e il processo continua fino alla fine del frame. Quando i quattro FIFO sincroni ricevono il segnale dell'evento di convalida, memorizzano i dati di riga e colonna (contenuti nei rispettivi registri) e il valore del sub-pixel (dato dal circuito di calcolo centrale) per formare una parola a 32 bit con l'evento xy coordinate da inviare, tramite 4 FIFO asincroni e un multiplexer, al computer host tramite l'interfaccia parallela o il collegamento seriale veloce. |

| I pixel in arrivo sono racchiusi in due finestre da 8X3 pixel: "Attuale" e "Precedente". Ad ogni impulso di clock si formano 8 finestre di 3X3 pixel facendo scorrere una casella di 3X3 pixel attraverso le ultime due colonne della finestra "Precedente" e l'intera finestra "Attuale". Il calcolo del centroide viene eseguito contemporaneamente su tutte le caselle. L'algoritmo fornisce una risoluzione di 1/32 di pixel. La figura mostra lo sheme dell'elaborazione centroide. |  |

SOFTWARE DI CONTROLLO

|

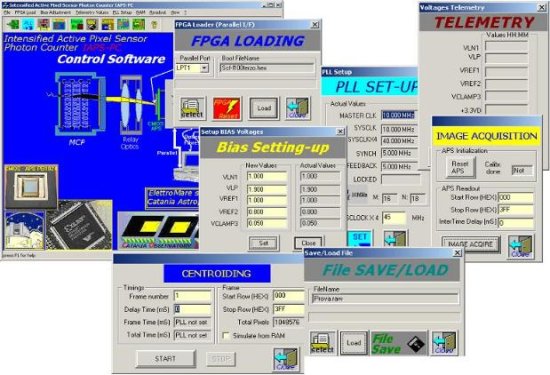

È stato sviluppato un software di controllo per guidare l'intera procedura di acquisizione. È scritto in Visual C ++ ed è organizzato come una serie di finestre di dialogo. Come si può vedere dalla figura seguente, la finestra di avvio contiene tutti i comandi disponibili che possono essere selezionati sia dal menu principale che dal menu delle icone. Il "CARICAMENTO FPGA" consente di configurare il FPGA, il "SET-UP PLL" consente di modificare la frequenza di lavoro, il "Setup BIAS" consente di impostare i livelli di tensione di polarizzazione dell'APS, la finestra di dialogo "TELEMETRIA", quando viene richiamato, visualizza i valori correnti dei bias, le due finestre di dialogo "ACQUISIZIONE IMMAGINI" e "SALVA / CARICA file" consentono di acquisire un'immagine e memorizzarla in un file. Infine il "CENTROIDING" consente di acquisire direttamente l'evento centroide durante il tempo di esposizione. |

PRIMI RISULTATI

|

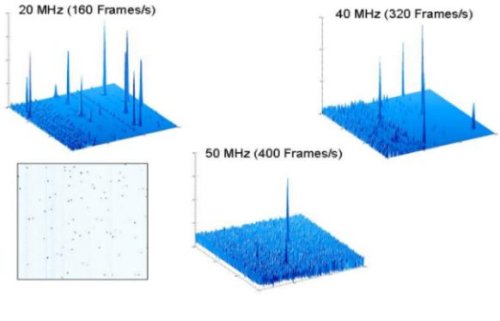

Prima di operare in modalità centroide, abbiamo acquisito molte immagini, variando il guadagno MCP, la messa a fuoco dell'obiettivo e la frequenza di lavoro dell'APS. Dall'analisi del profilo spot rispetto al livello di rumore abbiamo ricavato le migliori condizioni operative. Un'immagine di 512X512 pixel acquisita ad una frequenza di 20 MHz è mostrata nel pannello in basso a sinistra della figura Sono anche mostrati grafici di superficie di aree secondarie di 150 X 150 pixel di immagini scattate a 20 MHz, 40 MHz e 50 MHz. Come si può vedere, il rumore aumenta con l'aumentare della frequenza, mentre gli eventi sono sempre ben discriminati. Il rumore del pattern fisso APS misurato è trascurabile (3-6 ADU r. M. S.) A tutte le frequenze di lettura. È possibile ottenere una frequenza massima di 50 MHz (400 frame / s) senza influire sul rumore totale e quindi sul livello di discriminazione inferiore. Dalla finestra a mezzo frame il sistema funziona a 800 frame / se si ottiene una gamma dinamica più elevata. E così possiamo concludere che: il CMOS-APS utilizzato come sensore di posizione nei sistemi basati su MCP può funzionare meglio di un CCD più veloce e con alcuni importanti vantaggi: compattezza, semplicità, durezza delle radiazioni, basso consumo energetico, basso costo. |