CITIROC 1A

Citiroc 1A è un circuito integrato per applicazioni specifiche (ASIC) a 32 canali progettato per la lettura di SiPM.

Il chip consente di triggerare fino a un segnale pari ad 1/3 di p.e. e fornisce la misura della carica con una buona reiezione del rumore. Inoltre, il Citiroc 1A presenta in uscita i trigger dei 32 canali con un timing ad alta risoluzione (migliore di 100 ps).

Utilizzando un DAC per ogni canale è possibile regolare l'alta tensione applicata ai SiPM. Ciò consente una regolazione fine del guadagno dei SiPM in modo da correggere la non uniformità dei rivelatori in termini di tensione di breakdown e quindi variazioni di temperatura.

La misura del timing (jitter RMS di 100 ps) viene eseguita su un singolo fotoelettrone insieme alla misura della linearità dell'energia dell'1% fino a 2500 p.e. Il consumo di energia è 225mW quando tutti gli stadi sono ON.

|

TRL Technology Readiness Level |

8 - Full system using ASIC running |

|

Available versions |

Citiroc 1A : available |

|

Detector Read-Out |

SiPM, SiPM array |

|

Number of Channel |

32 |

|

Signal Polarity |

Positive |

|

Sensitivity |

Trigger on 1/3 photo-electron |

|

Timing Resolution |

better than 100ps RMS on single photo-electron |

|

Dynamic Range |

0-400 pC i.e 2500 photo-electrons @ 106 SiPM gain |

|

Packaging & Dimension |

|

|

Power Consumption |

225 mW when all stages on - supply voltage 3.3V |

|

Inputs |

32 voltage inputs with independant SiPM HV adjustments |

|

Outputs |

|

|

Internal Programmable Features |

|

|

Evaluation systems |

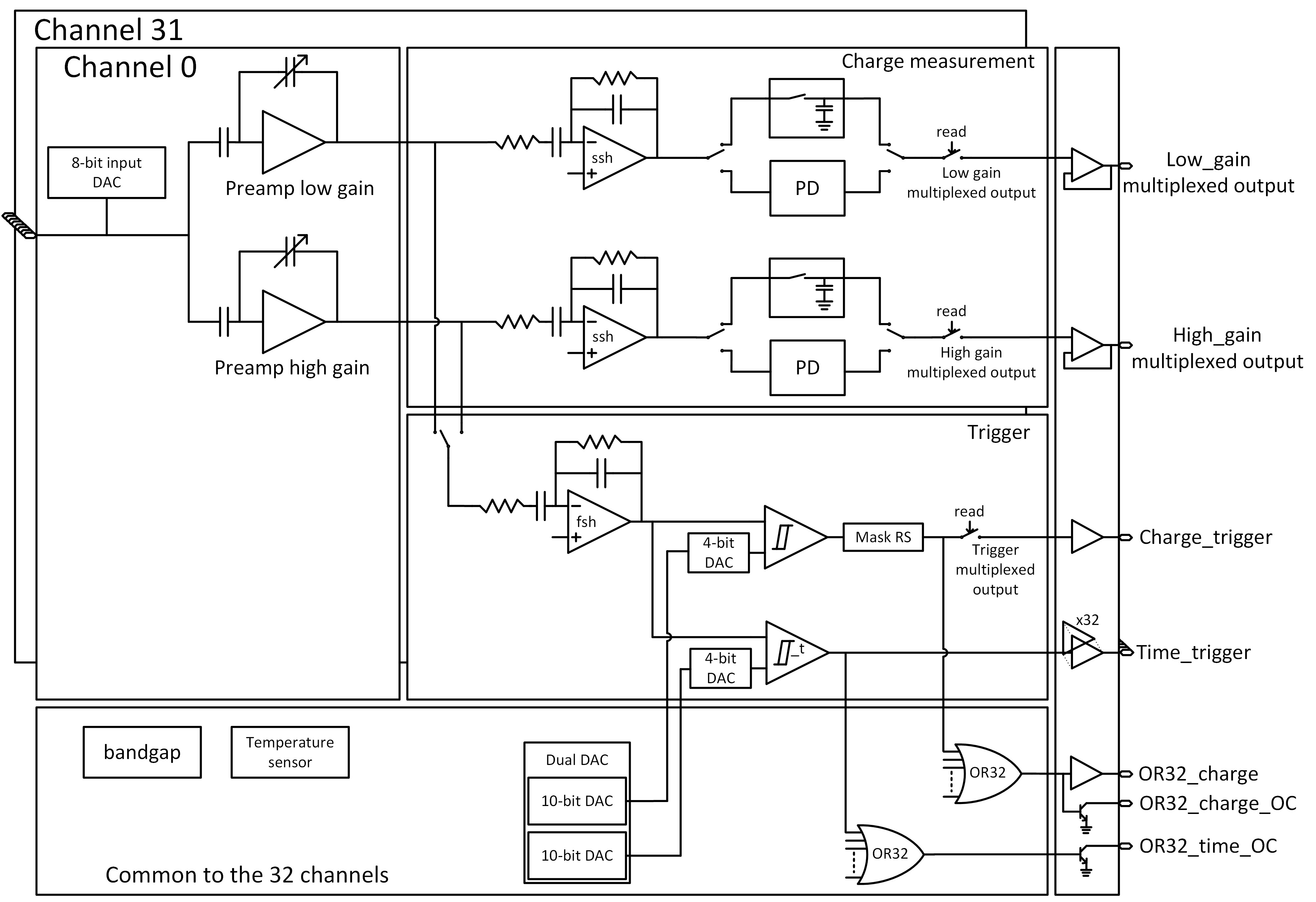

Di seguito lo schema relativo ai principali blocchi di condizionamento del segnale che caratterizzano un canale del CITIROC 1A

Ogni canale è caratterizzato da tre catene elettroniche separate in modo da amplificare il segnale ad alto guadagno (HG), basso guadagno (LG) e generare i trigger. L'impulso generato dal SiPM viene amplificato per mezzo di due preamplificatori programmabili e quindi derivato attraverso due circuiti di slow shaper dedicati uno per il preamplificatore ad alto guadagno e uno per quello a basso guadagno. I valori di guadagno possono essere scelti in modo da ottenere un intervallo dinamico da 0 a circa 60 fotoelettroni per il canale HG e da 0 a circa 2000 fotoelettroni per il canale LG.

Per la catena di trigger, un veloce shaper bipolare (FSH) collegabile selettivamente sia alla catena HG che a quella di G, genera un segnale veloce (tempo di shaping ~ 15 ns) collegato a un discriminatore programmabile a 10 bit per l'impostazione della soglia . L'uscita del discriminatore fornisce un segnale digitale (trigger) se il segnale di ingresso supera il livello di soglia.

Per il campionamento del segnale, il CITIROC è dotato di due modalità: il Peak Detector (PD) e l'SCA (Switched Capacitor Array), quest'ultima modalità è basata su una cella track & hold. Queste due modalità sono selezionabili tramite una linea di slow control. Il rilevatore di picco rileva il punto più positivo del segnale di ingresso in modo che il massimo dei segnali rappresenti la conversione dell'altezza dell'impulso dell'uscita del SiPM.